# ESCUELA SUPERIOR POLITÉCNICA DE CHIMBORAZO

## FACULTAD DE INFORMÁTICA Y ELECTRÓNICA

# ESCUELA DE INGENIERÍA ELECTRÓNICA EN TELECOMUNICACIONES Y REDES

"DISEÑO E IMPLEMENTACIÓN DE UN ROBOT ÁPODO (GUSANO) CONTROLADO INALÁMBRICAMENTE"

## **TESIS DE GRADO**

Previa la obtención del título de

### INGENIERO EN ELECTRÓNICA Y COMPUTACIÓN

Presentado por:

MAYRA ALEXANDRA AYALA VIMOS

RIOBAMBA – ECUADOR 2011

### Agradecimiento

Agradezco a la ESCUELA SUPERIOR POLITECNICA DE CHIMBORAZO, y a todos los docentes que me brindaron sus conocimientos y como personas su amistad sincera.

A mi tutor el Ing. Paul Romero por brindarme su apoyo, comprensión y conocimientos.

A todos mis *profes* no sólo de la carrera sino de toda la vida, mil gracias porque de alguna manera forman parte de lo que ahora soy.

Son muchas las personas especiales a quienes me gustaría agradecer su amistad, apoyo, ánimo y compañía en las diferentes etapas de mi vida. Algunas están aquí conmigo y otras en mis recuerdos y en el corazón. Sin importar en dónde estén o si alguna vez llegan a leer estas palabras quiero darles las gracias por formar parte de mí, por todo lo que me han brindado y por todas sus bendiciones.

Al más especial de todos, a ti Señor porque hiciste realidad este sueño, por todo el amor con el que me rodeas y porque me tienes en tus manos. Esta tesis es para ti.

#### **Dedicatoria**

A las personas más importantes de mi vida:

A Ti Mami, no me equivoco si digo que eres la mejor mamá del mundo, porque a pesar de las adversidades que tuve que enfrentar jamás tuve temor de hacerlo porque sabes qué? Ahí estabas tú para brindarme confianza y apoyo, porque cuando pensaba desfallecer bastaban tan solo palabras de amor para iluminar mi camino por eso y más; gracias Madre Amada por siempre.

A Ti Papi, éste es un logro muy importante que quiero compartir contigo, fueron tus recuerdos el motor principal que me impulsaron a alcanzar uno de mis sueños. Aunque no estuviste físicamente conmigo yo se que junto a ese ser tan hermoso que nos faculta la vida hiciste de mi lo que hoy soy.

Jordana Mayte, el amor de mi vida aunque todavía no puedes leer, un día vas a aprender y por eso también te dedico esta tesis, gracias por haber llegado cuando más te necesite, eres la bendición más grande de mi vida. Te Amo mi negrita.

Y a la persona más representativa de mi vida, mi tío Carlos Julio Bonifaz, quien fue padre, guía, amigo, el pilar importante en este logro tan ansiado. Este donde este mi corazón y gratitud por siempre y para siempre.

Por último dedico a todos los seres que luchan por alcanzar sus metas y creen que la educación abre las puertas de un mejor porvenir.

# Firmas de Responsabilidad

| NOMBRE                       | FIRMA | FECHA |

|------------------------------|-------|-------|

| Ing. Iván Menes              |       |       |

| DECANO DE LA FACULTAD DE     |       |       |

| INFORMÁTICA Y ELECTRÓNICA    |       |       |

| Ing. Pedro Infante           |       |       |

| DIRECTOR DE LA ESCUELA       |       |       |

| DE INGENIERÍA ELECTRÓNICA EN |       |       |

| TELECOMUNICACIONES Y REDES   |       |       |

| Ing. Paúl Romero             |       |       |

| DIRECTOR DE TESIS            |       |       |

| Ing. Edwin Altamirano        |       |       |

| MIEMBRO DEL TRIBUNAL         |       |       |

| Tlgo. Carlos Rodríguez       |       |       |

| DIRECTOR DEL CENTRO          |       |       |

| DE DOCUMENTACIÓN             |       |       |

| NOTA DE LA TESIS             |       |       |

# <u>Firma de Autoría</u>

"Yo, MAYRA ALEXANDRA AYALA VIMOS, soy responsable de las ideas, doctrinas y resultados expuestos en esta tesis; y, el patrimonio intelectual de la Tesis de Grado pertenece a la ESCUELA SUPERIOR POLITÉCNICA DE CHIMBORAZO".

Mayra Alexandra Ayala Vimos.

**AUTOR**

# Índice de Abreviaturas

ALU Unidad Aritmético Lógica.

A/D. Analógico/Digital.

ASK (Amplitude Shift Keying)Modulación por desplazamiento de Amplitud

CI. Circuito Integrado.

D/A. Digital/Analógico

E/S Entrada/Salida

EEPROM Memoria de solo lectura programable y borrable eléctricamente.

FAMOS Floating Gate Avalanche-Injection Metal Oxide Semiconductor

FLASH Memoria no volátil de bajo consumo.

FSK (Frecuency Shift Keying) Modulación por desplazamiento de Frecuencia

GPR Registros de propósito General.

HS Cristal de alta velocidad.

HSEROUT Salida serial de hardware asíncrono.

INTOSC Oscilador Interno.

I/O. Input/Output.

Led Diodo emisor de luz

LP Cristal para baja potencia y bajo consumo de corriente.

MCLR Master Clear (Reset).

MHz Megahercios.

Mbps Mega Bits por Segundo.

MHz. Megahercios

mA miliamperios

ms milisegundos

mV mili voltios

MPSK (Multiple Phase Shift Keying) Modulación por desplazamiento de Fase Multiple

OSC1/CLKIN Entrada del oscilador (cristal). Entrada de oscilador externo.

PIC Peripherical Interface Controller.

SFR Registros de Función Específica.

USART Transmisor/Receptor Asíncrono Universal.

Vcc Voltios de Corriente continúa

VCA Voltios de corriente Alterna

# **ÍNDICE GENERAL**

| <u>ÍNDICE GENERAL</u>                                     | 8 -  |

|-----------------------------------------------------------|------|

| <u>ÍNDICE DE FIGURAS</u>                                  | 14 - |

| <u>ÍNDICE DE TABLAS</u>                                   | 18 - |

| <u>CAPÍTULO I</u>                                         | 21 - |

| MARCO REFERENCIAL                                         | 21 - |

| 1. ANTECEDENTES                                           | 21 - |

| 2. JUSTIFICACIÓN                                          | 22 - |

| 3. OBJETIVOS                                              | 22 - |

| 1.3.1. OBJETIVO GENERAL                                   | 22 - |

| 1.3.2. OBJETIVOS ESPECIFICOS                              | 23 - |

| 4. HIPÓTESIS                                              | 23 - |

| <u>CAPÍTULO II</u>                                        | 24 - |

| FUNDAMENTO TEÓRICO                                        | 24 - |

| 2.1. LOCOMOCIÓN                                           | 24 - |

| 2.1.1. Introducción                                       | 24 - |

| 2.1.1.1. Tipos de locomoción                              | 26 - |

| 2.1.1.2. Locomoción de robots                             | 26 - |

| 2.1.1.3. Diseño de robots móviles                         | 27 - |

| 2.1.1.4. El problema de la locomoción                     | 28 - |

| 2.1.1.5. Robots ápodos                                    | 30 - |

| 2.2. SENSORES                                             | 31 - |

| 2.2.1. Introducción                                       | 31 - |

| 2.2.2. Criterios para la Selección de Sensores            | 31 - |

| 2.2.2.1. Sistemas Actuadores                              | 32 - |

| 2.2.2.2. Sistemas de Interfaz entre Sensores y Actuadores | 33 - |

| 2.2.3.    | Sensores Sharp                                            | 34 - |

|-----------|-----------------------------------------------------------|------|

| 2.2.4.    | Sensores Sharp en distintas familias.                     | 34 - |

| 2.2.4.1.  | Reflexivo IS471F                                          | 34 - |

| 2.2.4.2.  | Sharp GP2Y0A02YK                                          | 36 - |

| 2.2.4.3.  | La Familia GP2DXX                                         | 38 - |

| 2.2.4.4.  | El sensor GP2D12                                          | 40 - |

| 2.2.4.4.1 | . Curvas Características del GP2D12                       | 47 - |

| 2.3. L    | OS SISTEMAS DE COMUNICACIÓN                               | 49 - |

| 2.3.1.    | TRANSMISIÓN DE ONDAS DE RADIO                             | 49 - |

| 2.3.2.    | COMPONENTES DE UN SISTEMA DE COMUNICACIÓN                 | 52 - |

| 2.3.3.    | COMUNICACIÓN INALÁMBRICA                                  | 52 - |

| 2.3.3.1.  | Aspecto histórico y generalidades                         | 53 - |

| 2.3.3.2.  | Campos de Utilización                                     | 54 - |

| 2.3.3.3.  | Algunos problemas asociados con la tecnología inalámbrica | 54 - |

| 2.3.3.4.  | Equipo inalámbrico                                        | 54 - |

| 2.4. R    | ED INALÁMBRICA                                            | 55 - |

| 2.4.1.    | Categorías                                                | 55 - |

| 2.4.2.    | Aplicaciones                                              | 55 - |

| 2.5. R    | ADIOFRECUENCIA                                            | 56 - |

| 2.5.1.    | Características Generales                                 | 57 - |

| 2.5.2.    | Tipos de Comunicaciones Inalámbricas por RF               | 58 - |

| 2.6. M    | MOTORES                                                   | 58 - |

| 2.6.1.    | Servo Motores HITEC HS-311                                | 59 - |

| 2.6.1.1.  | Características                                           | 59 - |

| 2.6.1.2.  | Control                                                   |      |

| 2.6.1.3.  | Conexión                                                  |      |

| 2614      | Driver de Potencia para Control de Motores                | 61 - |

| <u>CAPÍTU</u> | <u> </u>                                            | 62 - |

|---------------|-----------------------------------------------------|------|

| MICRO         | CONTROLADORES APROPIADOS PARA EL CIRCUITO           | 62 - |

| 3.1.          | MICROCONTROLADORES                                  | 62 - |

| 3.1.1.        | Introducción                                        | 62 - |

| 3.1.2.        | Definición de Microcontrolador                      | 63 - |

| 3.1.3.        | Características de los Microcontroladores           | 64 - |

| 3.1.4.        | Tipos de Arquitecturas de Microcontroladores        | 64 - |

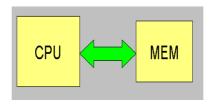

| 3.1.4.1.      | Arquitectura Von Neumann                            | 64 - |

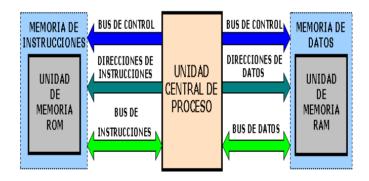

| 3.1.4.2.      | Arquitectura Harvard                                | 65 - |

| 3.1.5.        | Las Gamas de Pic                                    | 65 - |

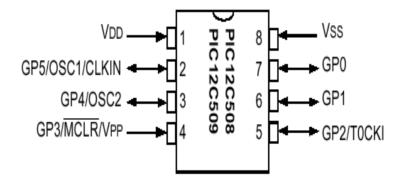

| 3.1.5.1.      | Gama Enana PIC12C (F) XXX                           | 66 - |

| 3.1.5.2.      | Gama Baja PIC16C5X                                  | 66 - |

| 3.1.5.3.      | Gama Media PIC16CXXX                                | 67 - |

| 3.1.5.4.      | Gama Alta PIC17CXXX                                 | 68 - |

| 3.1.6.        | Herramientas para el desarrollo de aplicaciones     | 68 - |

| 3.1.6.1.      | Ensamblador                                         | 69 - |

| 3.1.6.2.      | Compilador                                          | 69 - |

| 3.1.6.3.      | Simulador                                           | 69 - |

| 3.1.6.4.      | Programador                                         | 70 - |

| 3.1.6.5.      | Paquetes IDE                                        | 70 - |

| 3.2.          | MÉTRICAS PARA ELEGIR UN MICROCONTROLADOR            | 70 - |

| 3.2.1.        | Estudio de la mejor alternativa de microcontrolador | 71 - |

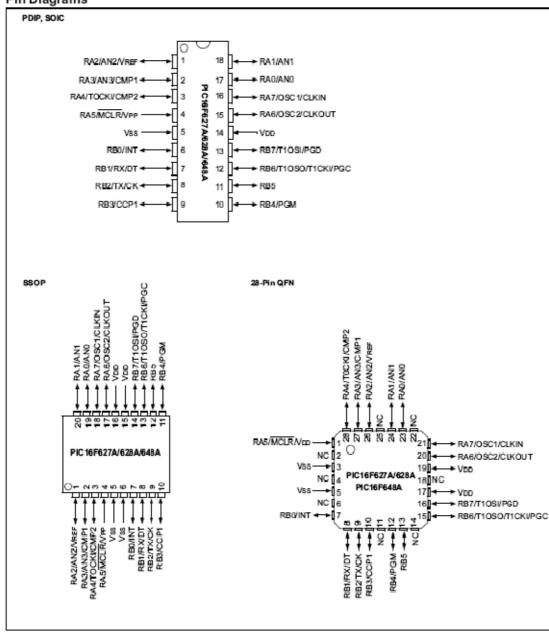

| 3.3.          | MICROCONTROLADOR 16F628A                            | 73 - |

| 3.3.1.        | Principales características                         | 73 - |

| 3.3.2.        | Características especiales:                         | 74 - |

| 3.3.3.        | Descripción de los terminales                       | 74 - |

| 3.3.3.1.      | Terminales de entrada-salida (16 en total)          | 74 - |

| 3.3.3.2.      | PORTA: RA0-RA7:                                                 | 75 - |

|---------------|-----------------------------------------------------------------|------|

| 3.3.3.3.      | PORTB: RB0-RB7:                                                 | 75 - |

| 3.3.3.4.      | Otros terminales                                                | 75 - |

| 3.3.4.        | Aspecto Interno del PIC 16F628                                  | 76 - |

| 3.3.5.        | El Procesador                                                   | 77 - |

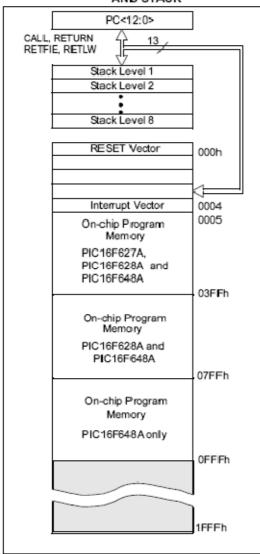

| 3.3.6.        | La Memoria de Datos                                             | 78 - |

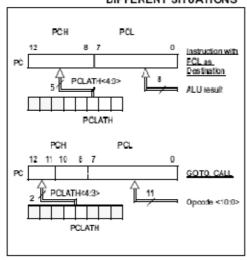

| 3.3.7.        | Direccionamiento de la Memoria de Datos                         | 79 - |

| 3.3.7.1.      | Direccionamiento Directo:                                       | 79 - |

| 3.3.7.2.      | Direccionamiento Indirecto:                                     | 79 - |

| 3.3.8.        | La memoria de Programa                                          | 79 - |

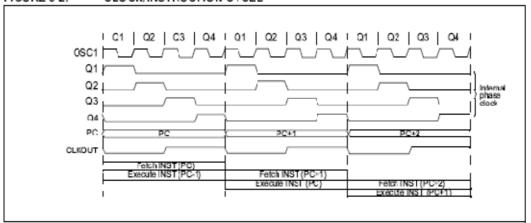

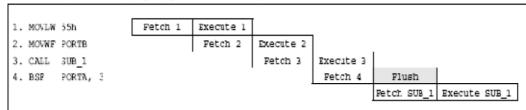

| 3.3.9.        | El Reloj                                                        | 80 - |

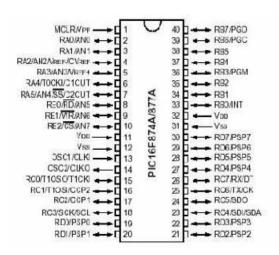

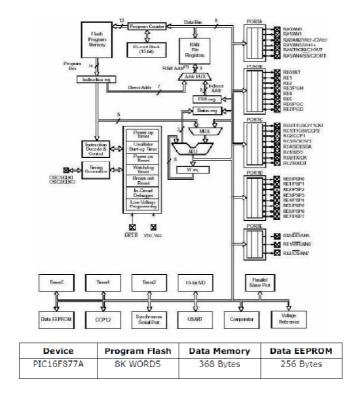

| 3.4.          | MICROCONTROLADOR 16F877A                                        |      |

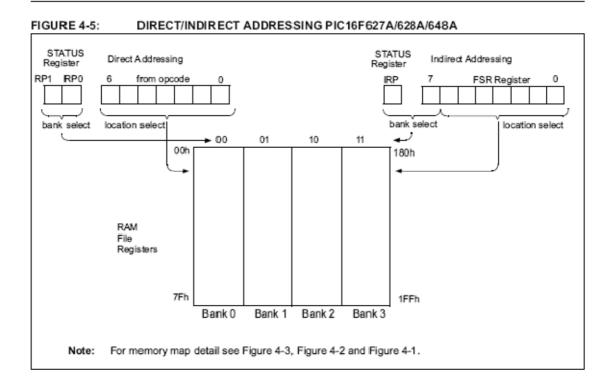

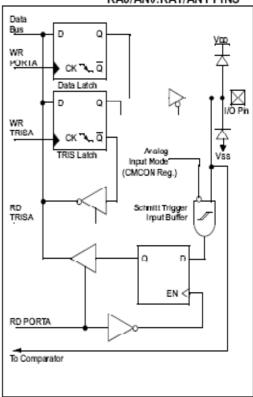

| 3.4.1.        | Puertos paralelos de entrada / salida del Pic 16f877a           | 82 - |

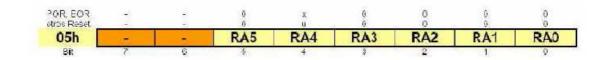

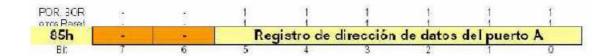

| 3.4.1.1.      | Puerto A (Porta)                                                | 82 - |

| 3.4.1.2.      | Puerto B (Portb)                                                | 83 - |

| 3.4.1.3.      | Puerto C (Portc)                                                | 84 - |

| 3.4.1.4.      | Puertos D y E                                                   | 85 - |

| 3.4.1.5.      | Puerto Serie Usart                                              | 85 - |

| 3.4.2.        | Configuración de la Usart del Pic 16F877A                       | 86 - |

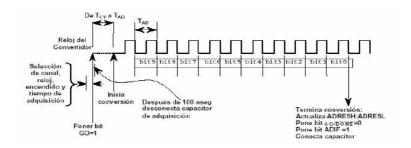

| 3.4.3.        | Proceso de Conversión Analógico/Digital                         | 86 - |

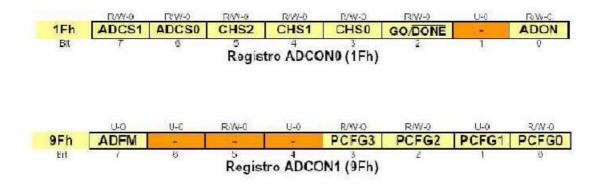

| 3.4.4.        | Registros de Control del Convertidor A/D del Pic 16F877A        | 87 - |

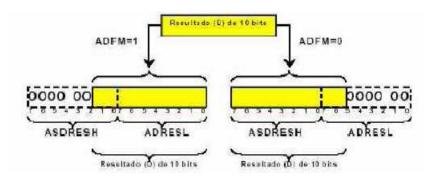

| 3.4.5.        | Los Registros de Resultados del Convertidor A/D del Pic 16f877a | 87 - |

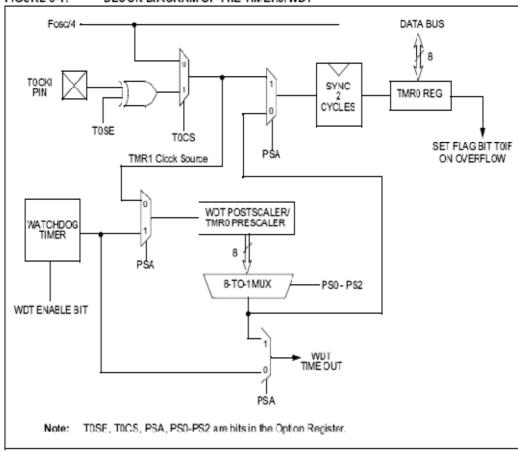

| 3.4.6.        | El Módulo Temporizador del Pic 16F877A                          | 88 - |

| <u>CAPÍTI</u> | <u>JLO IV</u>                                                   |      |

| DISEÑO        | O Y CONSTRUCCIÓN                                                | 89 - |

| 4.1. l        | ESQUEMA GENERAL DE FUNCIONAMIENTO                               | 89 - |

| 4.2. DISENO Y DESCRIPCION DE LOS BLOQUES QUE COMPONI     | EN EL SISTEMA |

|----------------------------------------------------------|---------------|

| DEL ROBOT ÁPODO                                          | 90 -          |

| 4.2.1. Etapa de procesamiento del Transmisor             | 90 -          |

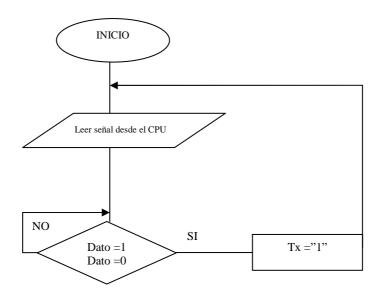

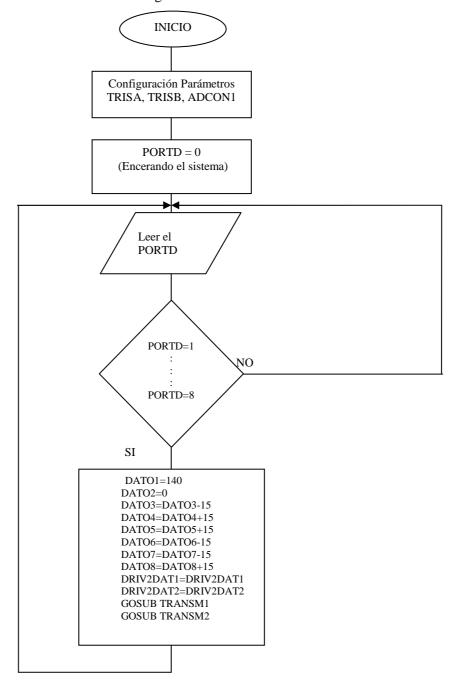

| 4.2.1.1. Algoritmo del Transmisor                        |               |

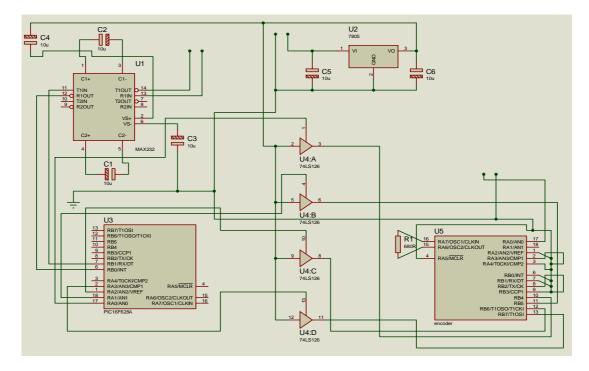

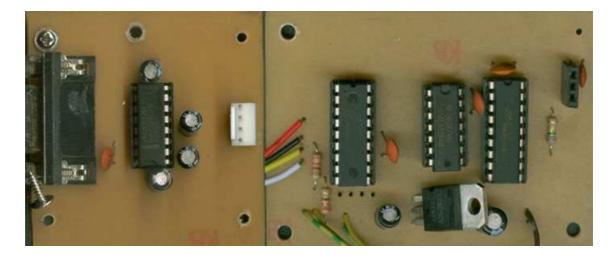

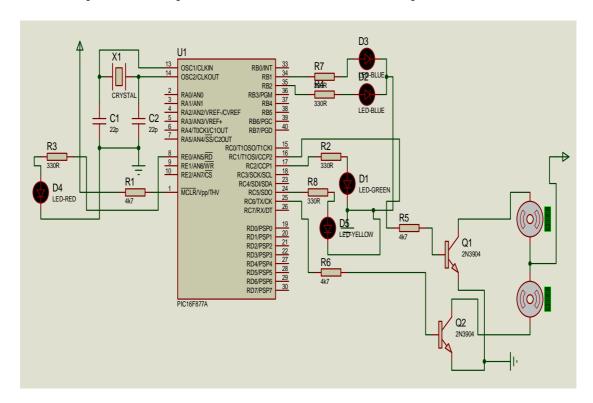

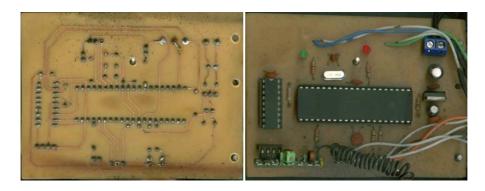

| 4.2.1.2. Circuito Transmisor Inalámbrico en Isis/Proteus | 91 -          |

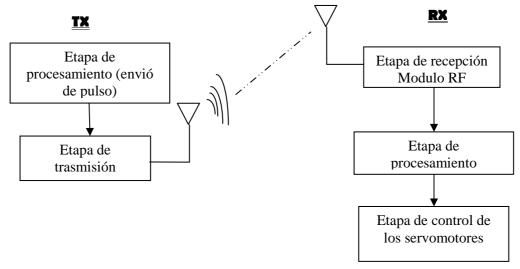

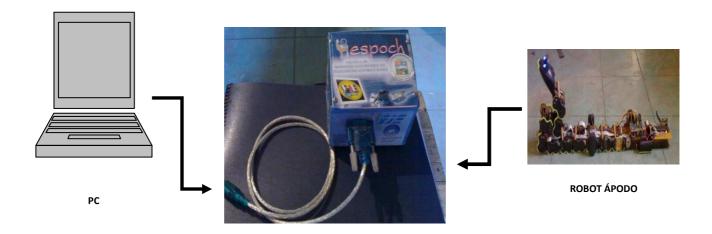

| 4.2.2. Etapa de Transmisión y Recepción                  | 92 -          |

| 4.2.3. Software De Transmisión De Datos                  | 93 -          |

| 4.2.4. Etapa de Procesamiento del Receptor               | 96 -          |

| 4.2.4.1. Algoritmo del Receptor                          | 97 -          |

| 4.2.4.2. Circuito Receptor Inalámbrico En Isis/Proteus   | 98 -          |

| 4.2.4.3. Etapa de Ejecución                              | 99 -          |

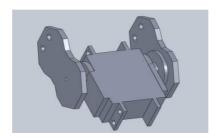

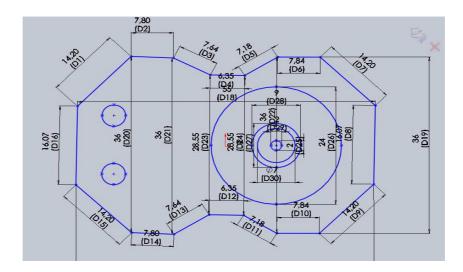

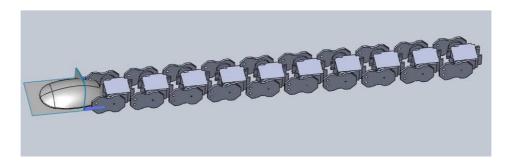

| 4.3. ESTRUCTURA Y DISEÑO DEL ROBOT                       | 100 -         |

| 4.3.1. Diseño del programa                               | 101 -         |

| <u>CAPÍTULO V</u>                                        | 102 -         |

| ANÁLISIS Y RESULTADOS                                    | 102 -         |

| 5.1. FUNCIONAMIENTO GENERAL                              | 102 -         |

| 5.1.1. Proceso de Comunicación                           | 102 -         |

| 5.1.2. Sistema de Locomoción                             | 102 -         |

| 5.1.3. Algoritmos de Control                             | 103 -         |

| 5.2. MOTORES UTILIZADOS                                  | 103 -         |

| 5.3. SENSOR INFRARROJO EMPLEADO                          | 104 -         |

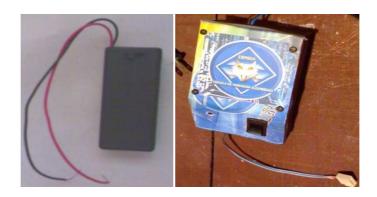

| 5.4. ALIMENTACIÓN PARA EL SISTEMA                        | 104 -         |

| 5.5. ENTORNO DE TRABAJO                                  | 105 -         |

| 5.6. ANÁLISIS ECONÓMICO                                  | 106 -         |

| 5.6.1. Costo de Materiales                               | 106 -         |

| 5.6.2. Presupuesto General                               | 107 -         |

| CONCLUSIONES                                             | 108 -         |

| RECOMENDACIONES | 109 - |

|-----------------|-------|

| RESUMEN         | 110 - |

| ABSTRACT        | 111 - |

| GLOSARIO        | 112 - |

| ANEXOS          | 117 - |

# ÍNDICE DE FIGURAS

| Figura II. 1 Ejemplos de robots con diferentes efectores para la locomoción terrestre | 25 - |

|---------------------------------------------------------------------------------------|------|

| Figura II. 2 Ejemplos de robots Ápodos.                                               | 31 - |

| Figura II. 3 Proceso de Adquisición de Datos                                          | 33 - |

| Figura II. 4 Ejemplo de Sensor Reflexivo.                                             | 35 - |

| Figura II. 5 Funcionamiento del Sensor.                                               | 35 - |

| Figura II. 6 Dimensiones del Sensor.                                                  | 36 - |

| Figura II. 7 Sensor Sharp.                                                            | 37 - |

| Figura II. 8 Esquema interno y dimensiones del Sensor.                                | 37 - |

| Figura II. 9 Incidencia del haz de Luz.                                               | 39 - |

| Figura II. 10 Sharp GP2D12 y su conector de tres pines.                               | 40 - |

| Figura II. 11 Detalle del conector del Sensor.                                        | 41 - |

| Figura II. 12 Triangularización.                                                      | 42 - |

| Figura II. 13 Reflexión del Haz de Luz.                                               | 43 - |

| Figura II. 14 Dimensiones y Encapsulado.                                              | 43 - |

| Figura II. 15 Bloques Internos.                                                       | 46 - |

| Figure II 16 Cronograms                                                               | 16   |

| Figura II. 17 Características de Distancias47                                               | - |

|---------------------------------------------------------------------------------------------|---|

| Figura II. 18 Tensión de Salida Analógica en función de Superficie Iluminada del Objeto     |   |

| Reflexivo 47                                                                                | - |

| Figura II. 19 Tensión de Salida Analógica en función de la Distancia al objeto reflexivo 48 | - |

| Figura II. 20 Tensión de Salida Analógica en función de la Temperatura Ambiente48           | - |

| Figura II. 21 Tensión de Salida Analógica en función de la distancia de detección 49        | - |

| Figura II. 22. Reflexión de las ondas en la ionosfera 49                                    | - |

| Figura II. 23. Sistema de comunicación 52                                                   | - |

| Figura II. 24. Servomotor59                                                                 | - |

| Figura II. 25. Ancho de Pulso60                                                             | - |

| Figura II. 26. Conexión del Servo61                                                         | - |

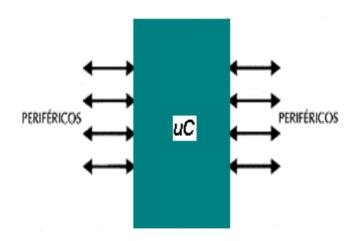

| Figura III. 27. Microcontrolador y Periféricos 63                                           | - |

| Figura III. 28. Arquitectura Von Neumann65                                                  | - |

| Figura III. 29. Arquitectura Harvard 65                                                     | - |

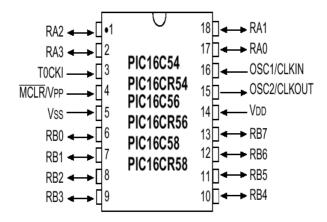

| Figura III. 30. Diagrama de conexiones de los PIC12Cxxx de la gama enana66                  | - |

| Figura III. 31. Diagrama de conexiones de los PIC16C54/56 de la gama baja 67                | - |

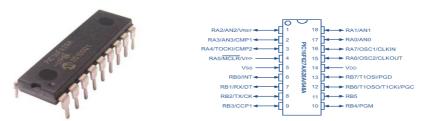

| Figura III. 32. Diagrama de conexiones del PIC16C74, de la gama media 67                    | - |

| Figura III. 33. Encapsulado del PIC 16f62873                                                | - |

| Figura III. 34. Diagrama de pines 16F62874                                                  | - |

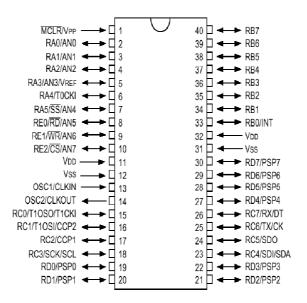

| Figura III. 35. Pines del PIC 16F877A81 -                                     |

|-------------------------------------------------------------------------------|

| Figura III. 36. Arquitectura Interna del Pic 16F877A81 -                      |

| Figura III. 37. Registro PORTA (05H)82 -                                      |

| Figura III. 38. Registro TRISA (85H)83 -                                      |

| Figura III. 39. Conversión Analógico/Digital del PIC 16F877A                  |

| Figura III. 40. Registros de Control del convertidor A/D del PIC 16F877A 87 - |

| Figura III. 41. Registros de Resultados del Convertidor A/D87 -               |

| Figura IV. 42. Diagrama General del Sistema89 -                               |

| Figura IV. 43. Diagrama de flujo para la transmisión de información91 -       |

| Figura IV. 44. Diagrama esquemático del transmisor91 -                        |

| Figura IV. 45. Diseño del transmisor. ————————————————————————————————————    |

| Figura IV. 46. Transmisor93 -                                                 |

| Figura IV. 47. Pantalla Principal93 -                                         |

| Figura IV. 48. Ingreso del Puerto94 -                                         |

| Figura IV. 49. Puerto Habilitado94 -                                          |

| Figura IV. 50. Secuencias de Desplazamiento95 -                               |

| Figura IV. 51. Esquema de Conexión de la Placa de Comunicación Serial96 -     |

| Figura IV. 52. Diagrama de flujo para la recepción de información97 -         |

| Figura IV. 53. Diagrama esquemático del receptor98 -                          |

| Figura IV. 54. Diseño del Receptor99                 | € - |

|------------------------------------------------------|-----|

| Figura IV. 55. Diagrama de la etapa de ejecución99   | ) - |

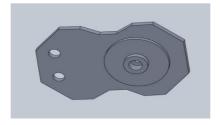

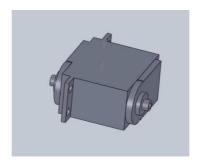

| Figura IV. 56. Estructura Lateral100                 | ) - |

| Figura IV. 57. Estructura del Eje Falso 100          | ) - |

| Figura IV. 58. Estructura de cada Articulación 100   | ) - |

| Figura IV. 59. Dimensiones de la Pieza Principal 101 | 1 - |

| Figura IV. 60. Estructura del Robot101               | 1 - |

| Figura V. 61. Servomotor HITEC HS-311103             | 3 - |

| Figura V. 62. Sensor SHARP GP2D120X 104              | 1 - |

| Figura V. 63. Fuentes de alimentación 105            | 5 - |

| Figura V. 64. Detección de obstáculos105             | 5 - |

# ÍNDICE DE TABLAS

| Tabla II. I. Calificaciones Máximas Absolutas                | 36 -  |

|--------------------------------------------------------------|-------|

| Tabla II. II. Calificaciones Máximas Absolutas               | 37 -  |

| Tabla II. III. Modelos de las Familias Sharp                 | 38 -  |

| Tabla II. IV. Valores Máximos Absolutos                      | 44 -  |

| Tabla II. V. Condiciones de Trabajo Recomendadas             | 44 -  |

| Tabla II. VI. Características Electro- Ópticas               | 45 -  |

| Tabla II. VII. Características de las capas de la tierra     | 51 -  |

| Tabla II. VIII. Características de las capas de la tierra    | 59 -  |

| Tabla II. IX. Asignación cuantitativa para las métricas      | 71 -  |

| Tabla II. X. Calificaciones y costos                         | 72 -  |

| Tabla II. XI. Matriz de puntos                               | 73 -  |

| Tabla II. XII. Modulo del Temporizador del PIC 16F877A       | 88 -  |

| Tabla II. XIII Materiales empleados en el robot y sus costos | 106 - |

| Tabla II. XIV. Tabla Presupuesto General                     | 107 - |

# INTRODUCCIÓN

Desde la invención del circuito integrado, el desarrollo constante de la electrónica digital ha dado lugar a dispositivos cada vez más complejos. Entre ellos los microprocesadores y los microcontroladores. Estos se utilizan en circuitos electrónicos comerciales desde hace unos años de forma masiva, debido a que permiten reducir el tamaño y el precio de los equipos. En los últimos años se ha facilitado enormemente el trabajo con los microcontroladores al bajar los precios, aumentar las prestaciones y simplificar los montajes, de manera que en muchas ocasiones vale la pena utilizarlos en aplicaciones donde antes se utilizaba lógica discreta.

El ser humano lleva siglos soñando con las creaciones de robots autónomas y obedientes, capaces de llevar a cabo los trabajos más duros. A finales del siglo XX ese sueño comenzó a ser real. Los robots ya han demostrado ser excelentes sustitutos de los humanos para llevar a cabo tareas repetitivas que no requieran capacidad de improvisación. Ya hay numerosos robots trabajando en minas y excavaciones petrolíferas, fabricando bienes de consumo en cadenas de montaje, explorando el espacio y combatiendo en guerras. Por otro lado hay muchos trabajos que las personas no les gusta hacer, sea ya por ser aburrido o bien peligroso, siempre se va a tratar de evitar para no hacerlo.

Mediante un microcontrolador PIC, podemos realizar diferentes máquinas electrónicas que incluso puedan sustituir el trabajo humano. Además de ello también podemos hablar de robots que puedan ayudar en áreas poco accesibles por el hombre, entre ellos tenemos un robot ápodo tipo gusano donde el principal objetivo es sobrepasar los obstáculos que se encuentren enfrente de su trayectoria de movimiento. Para ello, el microcontrolador que controla el robot, utilizará un sensor de donde obtendrá lecturas, de su trayectoria de movimiento, La solución a la problemática planteada se puede dividir en "hardware" y en "software".

El presente trabajo de investigación se encuentra dividido en cinco capítulos para el análisis del DISEÑO Y CONSTRUCCIÓN DE UN ROBOT ÁPODO TIPO GUSANO, los que se detallan a continuación:

Capítulo I.- En este capítulo se especifica los antecedentes, la debida justificación y los objetivos de la realización de esta tesis.

Capítulo II y III.- En estos capítulos teóricamente se establecen los tipos de sensores, actuadores, microcontroladores, baterías y demás conceptos de los elementos que se utilizan posteriormente.

Capítulo IV.- Este capítulo contiene los pasos a considerar para el diseño y construcción del robot.

Capítulo V.- En este capítulo se detallará el Análisis respectivo así como los Resultados obtenidos en la implementación de la tesis.

Esta estructura permitirá arribar a conclusiones y proponer recomendaciones fundamentadas en el proceso de investigación realizado.

# **CAPÍTULO I**

#### **MARCO REFERENCIAL**

#### 1. ANTECEDENTES

En los últimos años, los robots ápodos han cobrado interés en el área de robótica móvil. Esto se debe a que este tipo de robots, que se valen únicamente de su cuerpo para moverse, tienen un sistema de locomoción robusto para contender con ambientes con superficies irregulares.

Los robots ápodos están frecuentemente inspirados en la naturaleza, sus patrones se basan en los movimientos de los gusanos y serpientes cuya estructura se compone de múltiples segmentos que permiten el movimiento ondulatorio.

El presente proyecto apunta a implementar un robot gusano (diseño, construcción y desarrollo de hardware y software), el cual, como su nombre lo dice, simulará el movimiento de este invertebrado basado en la utilización de servomotores y diversas secuencias de control. El robot se desplazará con movimiento ondulatorio por trayectos rectos sin la utilización de ruedas y/o

patas. El mismo podrá ser utilizado en espacios y ambientes difícilmente accesibles para el ser humano, ya sea por su peligrosidad o por su tamaño.

Las secuencias de desplazamiento serán controladas por medio de microcontroladores.

#### 2. JUSTIFICACIÓN

Un robot ápodo se destaca por la ausencia de extremidades obligándole a realizar movimientos ondulatorios con su cuerpo. Este proyecto diseñará e implementará un robot ápodo tipo gusano cuyas articulaciones estarán formadas por una concatenación de servomotores controlados inalámbricamente, utilizando un módulo de radiofrecuencia. Para lo cual se utilizará como módulo principal un microcontrolador que manipulara las distintas articulaciones.

Además se utilizará un sensor infrarrojo con el fin de detectar obstáculos.

Esta es una alternativa para mejorar el desplazamiento de los robots en caminos con desniveles.

Al comparar el desempeño del robot gusano con otros esquemas de desplazamiento, el robot ápodo brinda una mayor flexibilidad al momento de sobrepasar los obstáculos mas no los evade.

Podría ser utilizado en la participación de eventos relacionados a la robótica, etc.

#### 3. OBJETIVOS

#### 1.3.1. OBJETIVO GENERAL

✓ Diseñar e implementar un robot ápodo (tipo gusano) controlado inalámbricamente

#### 1.3.2. OBJETIVOS ESPECIFICOS

- ✓ Desarrollar un sistema de comunicación inalámbrico confiable que permita un adecuado control del robot.

- ✓ Estudiar las posibles secuencias de control de movimiento del robot.

- ✓ Implementar algoritmos y programas de control para las secuencias de desplazamiento.

- ✓ Implementar la estructura del robot basándonos en el diseño elaborado.

- ✓ Realizar pruebas y puesta a punto del robot.

## 4. HIPÓTESIS

Con el diseño y construcción de un robot ápodo se pretende lanzar una alternativa diferente en cuanto a desplazamiento se refiere. Es decir que proporcione mayor flexibilidad al momento de detectar los obstáculos sobrepasándolos y no evadiéndolos.

# CAPÍTULO II

#### **FUNDAMENTO TEÓRICO**

#### 2.1. LOCOMOCIÓN

#### 2.1.1. Introducción

La locomoción es la capacidad que tienen los seres vivos pertenecientes al reino animal que les permite trasladarse voluntariamente de un lugar a otro. Es una de las características diferenciadoras de los animales con respecto a las plantas. Hay dos aspectos importantes a tener en cuenta: el **control** y la **voluntariedad**. Para que el movimiento sea considerado locomoción el individuo tiene que querer realizarlo y además controlarlo. Así, los nenúfares que reposan sobre la superficie del agua se mueven por las corrientes o la acción de otros animales, pero no se considerará locomoción ya que no son voluntarios ni controlados.

Figura II. 1 Ejemplos de robots con diferentes efectores para la locomoción terrestre.

El estudio de la locomoción se divide en dos niveles:

El nivel inferior es el encargado del control y la coordinación de los músculos (o actuadores en el caso de los robots) para que el individuo pueda desplazarse. Engloba también los diferentes tipos de maneras de desplazarse que se pueden lograr (giros, desplazamiento en línea recta, desplazamiento lateral, etc.). Las preguntas que se resuelven en este nivel son: ¿Cómo me desplazo? ¿Cómo coordino todos los músculos (actuadores) para lograr la locomoción?

El nivel superior se encarga de la planificación de trayectorias, navegación y otras tareas de mayor nivel. Está relacionado con la voluntariedad. Las preguntas que definen este nivel son: ¿Dónde quiero ir? ¿Qué camino seguir?

En esta tesis nos centraremos en el nivel inferior de la locomoción, estudiando los mecanismos para que los robots ápodos puedan desplazarse.

#### 2.1.1.1. Tipos de locomoción

En la naturaleza, la locomoción de los animales se ha adaptado al medio en el que viven. Se puede realizar una primera clasificación según el medio en el que se desplazan. Así, la locomoción puede ser: aérea, acuática o terrestre. Esta clasificación no es excluyente. Los mamíferos terrestres también son capaces de desplazarse cortas distancias por el agua, por ejemplo para cruzar un río. En este caso utilizan un modo de caminar diferente, que les permite nadar.

La locomoción terrestre se puede dividir a su vez en dos categorías, según los órganos empleados para realizar el desplazamiento: locomoción mediante patas (mamíferos, insectos) o mediante movimientos corporales (serpientes, orugas, lombrices).

#### 2.1.1.2. Locomoción de robots

Una de las áreas de investigación en robótica es la locomoción: dotar a los robots de capacidades locomotivas para que puedan trasladarse de un lugar a otro. Estos robots reciben el nombre genérico de robots móviles. A su vez, el estudio de la locomoción se realiza en los dos niveles mencionados en los apartados previos. En las investigaciones del nivel superior se parte de que el robot puede desplazarse, haciéndose abstracción de los mecanismos para que sea posible (patas, ruedas...) y se centra en las tareas de alto de nivel de navegación, planificación de trayectorias, visión, cooperación, etc.

Al igual que sucede con los animales, en el estudio del nivel inferior de la locomoción se pueden clasificar los robots según los efectores empleados para su desplazamiento: ruedas, orugas, patas o el cuerpo. Bajo el término robots ápodos quedan englobados aquellos robots, que igual que sus homólogos en la naturaleza, realizan la locomoción mediante movimientos corporales. Estos son las cuatro categorías clásicas para el estudio de la locomoción, sin embargo la clasificación no es cerrada. En la figura 2.1 se muestran fotos de robots que usan diferentes efectores para realizar la locomoción: Ruedas, orugas, Whegs, el cuerpo y cuatro, seis y ocho patas.

Los temas de investigación en el nivel inferior de la locomoción son las propiedades de los diferentes efectores, cómo realizar la coordinación de los actuadores, los diferentes modos de caminar, algoritmos de control, etc.

#### 2.1.1.3. Diseño de robots móviles

Lo mismo que ocurre en el reino animal, donde la locomoción de los individuos está especialmente adaptada al entorno en el que normalmente se desenvuelven, para el diseño de un robot móvil es esencial conocer el terreno por el que se va a desplazar. Es el entorno el elemento clave en la decisión de qué efectores elegir y qué tipos de modo de caminar implementar. Así por ejemplo, si el robot se va a desplazar por superficies lisas donde no existe la necesidad de superar obstáculos, bastará con utilizar ruedas o a lo sumo orugas.

El proceso de diseño se podría resumir en los siguientes pasos:

- 1. Estudiar el entorno en el que se va desplazar el robot

- 2. Seleccionar los efectores

- 3. Implementar los modos de caminar

Estos pasos son muy críticos. Una mala elección a este nivel, implicaría tener que volver a reconstruir el robot. Esta es la razón por la que las investigaciones a este nivel son tan importantes: cuanto mejor se conozcan las propiedades de los efectores, los modos de caminar posibles, la eficiencia de cada modo de caminar, etc., mayor serán los datos disponibles para tomar una decisión de diseño correcta.

Leger abordó en su tesis doctoral el problema del diseño automático de robots, utilizando un enfoque evolutivo. Su idea central es que el espacio de búsquedas de soluciones al problema de la locomoción es tan amplio que son necesarias herramientas que permitan explorar la mayor cantidad posible de ellas antes de tomar una decisión de qué diseño implementar. Un error en la configuración del robot a este nivel es muy crítico. Por ello propuso utilizar algoritmos evolutivos para ayudar a los diseñadores en esta etapa.

Sin embargo, existen aplicaciones en las que es difícil conocer a priori y con detalle el terreno, por lo que hay mucha incertidumbre en la etapa inicial de diseño. Tal es el caso del diseño de robots para las operaciones de búsqueda y rescate o la exploración de planetas. Debido a ello, el robot tiene que tener la máxima versatilidad posible. Las investigaciones se centran en estudiar los efectores más versátiles y los diferentes modos de caminar posibles.

#### 2.1.1.4. El problema de la locomoción

Uno de los grandes retos es el de desarrollar un robot que sea capaz de moverse por cualquier tipo de entorno por muy escarpado y complicado que sea. Es decir, un robot con una gran versatilidad.

Esto tiene especial interés en las aplicaciones en las que el entorno no es lo suficientemente conocido o es cambiante, como en la exploración de las superficies de otros planetas, exploración en entornos hostiles o operaciones de búsqueda y rescate. ¿Qué es mejor utilizar, patas, rudas, orugas...? ¿Qué número de patas? ¿Qué tipo de movimiento? ¿Qué configuración de las patas si es que las tiene?

La Nasa está especialmente interesada en este problema, financiando proyectos destinados a la construcción y evaluación de alternativas para que los robots se puedan desplazar en entornos escarpados.

Dos de estos proyectos en la etapa inicial (finales de los ochenta) fueron el CMU Ambler y el Dante II. Son dos ejemplos que ilustran el modelo de diseño descrito en el apartado anterior: diseños de estructuras específicas a partir de las especificaciones del entorno.

El Ambler es un robot autónomo para la exploración de planeta, pensado para moverse por la superficie de Marte. A partir de las especificaciones se diseñó el robot, dotado de 6 patas, 3.5m de altura y un peso de 2.500Kg. El tipo de locomoción seleccionado fue mediante patas, es el que presenta mayor eficiencia teórica. Sin embargo, este robot nunca fue enviado a Marte. Para cumplir con los requisitos, las dimensiones y peso del robot son excesivamente grandes. A parte de que el consumo de potencia es muy alto.

El Robot Dante II se diseñó también para explorar terrenos escarpados y se probó en 1994 para la exploración del volcán del monte Spurr en Alaska. En este caso, el robot poseía 8 patas con un sistema de locomoción denominado framewalker. A pesar de que se conocían las especificaciones del terreno, que el robot poseía un cable que lo mantenía enganchado a la cima y por el que iba descendiendo, al quinto día volcó y no pudo ser recuperado.

Para la exploración de Marte, la Nasa se decantó por la utilización de ruedas ya que hasta el momento han dado muy buenos resultados. Sin embargo, las rudas son muy limitadas. Sólo permiten que el robot se pueda desplazar por entornos muy controlados. Es una de las razones por las que es necesario planear con mucha antelación y cuidado el lugar al que se enviarán los robots, no sólo teniendo en cuenta el interés en la recolección de datos científicos, las condiciones atmosféricas... sino también que los robots puedan desplazarse correctamente por el terreno. Esto es una gran limitación.

#### 2.1.1.5. Robots ápodos

Frente a la locomoción terrestre mediante patas, están los seres vivos que utilizan movimientos corporales. Los robots que utilizan este tipo de desplazamiento los denominaremos robots ápodos. El término ápodo significa "carente de patas".

Estos robots tienen unas características que los hacen únicos, al igual que sus homólogos las serpientes y gusanos. Por un lado está su capacidad para cambiar su forma. Frente a las rígidas estructuras del resto de robots, los ápodos pueden doblarse y adoptar la forma del terreno por el que se desplazan.

Por otro lado, su sección es muy pequeña en comparación con su tamaño, lo que les permite introducirse por tubos u orificios pequeños y llegar a lugares donde otros robots no pueden.

Figura II. 2 Ejemplos de robots Ápodos.

#### 2.2. SENSORES

#### 2.2.1. Introducción

Los sensores de proximidad tienen mucha relevancia en el mundo de la industria debido a la preocupación en lo referente a la seguridad, tanto de personas como de la maquinaria.

A continuación se realizara la descripción del funcionamiento del sensor usado en la medición de proximidad en este caso el GP2D120.

#### 2.2.2. Criterios para la Selección de Sensores

#### Sensibilidad

Se define como el cociente entre la tasa de cambio de valores de salida para el cambio los valores de entrada.

#### Linealidad

• Es la medida de la constancia de la tasa de salida con respecto a la entrada.

#### Rango

• Es la medida de la diferencia entre el mínimo y el máximo valor medido.

#### Tiempo de Respuesta

Puede ser un tiempo fijo o depender de cuánto varíe la magnitud a medir. Depende de la capacidad del sistema para seguir las variaciones de la magnitud de entrada.

#### Precisión

• Es el error de medida máximo esperado.

#### Repetitividad

• Error esperado al repetir varias veces la misma medida.

#### Resolución

• Mínima variación de la magnitud de entrada que puede apreciarse a la salida.

#### 2.2.2.1. Sistemas Actuadores

Se les llama así a todo circuito, interfaz o motor, que ejecute una determinada acción o tarea en función de las entradas que nos otorguen los sensores.

Por ejemplo el robot tiene sistemas que le permitan moverse, según la información que se ha recibido del medio externo por medio de los sensores, permitiendo que el mismo llegue a cumplir la misión para el cuál fue diseñado desde un principio. Todo lo que le permita al robot reaccionar ante el medio externo cualquiera que sea este y cualquiera que sea el propósito para el que fue diseñado, se le conoce como actuador.

La salida de un actuador puede ser de varias formas:

- Movimiento mecánico

- Tensión

- Corriente

- Presión

- Nivel hidráulico

- Intensidad luminosa, etc.

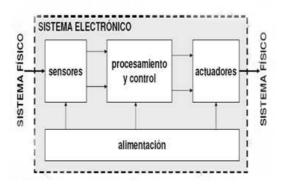

#### 2.2.2.2. Sistemas de Interfaz entre Sensores y Actuadores

Para que los sensores y actuadores cumplan su función e interactúen entre sí se necesita de un sistema, que informe a los actuadores que es lo que deben hacer en función de la información que ha sido recibida por los sensores, está interfaz es diseñada para trabajar con datos de ingreso que nos otorgan los sensores y salidas que manejan los diferentes actuadores.

#### Sistema electrónico

Figura II. 3 Proceso de Adquisición de Datos.

Esta interfaz que es un sistema de control de entradas y salidas, se han realizado para mayor facilidad y mejor control en los llamados microcontroladores, que permiten la ejecución de

múltiples tareas y procesos en un simple chip, lo cual reduce considerablemente los componentes electrónicos y el tamaño del diseño que antes se utilizaba.

#### 2.2.3. Sensores Sharp.

Nos centraremos en los sensores infrarrojos Sharp y después pasaremos a explicar la familia GP2Dxx que es una de las familias más utilizadas tanto en lo que viene a denominarse robótica móvil casera como en el ámbito de la investigación debido principalmente a su facilidad de integración y su bajo coste.

Es importante destacar que hemos decido explicar algunos sensores diferentes de la familia GP2Dxx para observar que no es la única familia utilizada por Sharp.

Finalmente hemos centrado nuestra atención en el sensor GP2D12.

#### 2.2.4. Sensores Sharp en distintas familias.

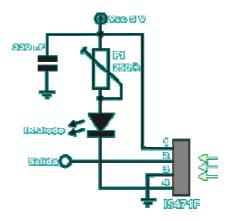

#### **2.2.4.1.** Reflexivo IS471F

Sensor basado en el dispositivo SHARP IS471F inmune a interferencias de luz normal. Este sensor incorpora un modulador/demodulador integrado en su carcasa ya a través de su patilla 4 controla un diodo LED de infrarrojos externo, modulando la señal que este emitirá, para ser captada por el IS471F que contiene el receptor. Cuando un objeto se sitúa enfrente del conjunto emisor/receptor parte de la luz emitida es reflejada y re modulada para activar la salida en la patilla 2 que pasará a nivel bajo si la señal captada es suficientemente fuerte.

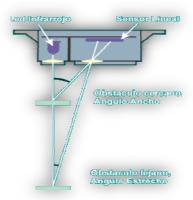

Figura II. 4 Ejemplo de Sensor Reflexivo.

El uso de la luz infrarroja modulada tiene por objeto hacer al sensor relativamente inmune a las interferencias causadas por la luz normal de una bombilla o la luz del sol.

El funcionamiento de este sensor se observa en el siguiente esquema. El sensor se alimenta por las patillas 1 y 3 que corresponden a Vcc y Gnd respectivamente. La patilla 2 es la salida del detector y la patita 4 es la salida que modula al diodo LED externo. Mediante el potenciómetro P1 se varía la distancia a la que es detectado el objeto. Cuando más baja sea la resistencia de este potenciómetro, más intensa será la luz emitida por el diodo de infrarrojo y por lo tanto mayor la distancia a la que puede detectar el objeto.

Figura II. 5 Funcionamiento del Sensor.

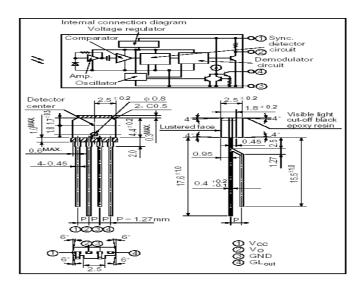

Figura II. 6 Dimensiones del Sensor.

| Parameter                |                | Symbol           | Rating       | Unit |

|--------------------------|----------------|------------------|--------------|------|

| Supply voltage           |                | V <sub>cc</sub>  | -0.5 to 16   | V    |

| Output                   | Output voltage | Vo               | 16           | V    |

|                          | Output current | Io               | 50           | mA   |

| *1 GL output             | Output voltage | $V_{GL}$         | 16           | V    |

| Power dissipation        |                | P                | 250          | mW   |

| Operating temperature    |                | Торг             | -25 to +60   | °C   |

| Storage temperature      |                | T <sub>stg</sub> | - 40 to +100 | °C   |

| *2 Soldering temperature |                | Tsol             | 260          | °C   |

Tabla II. I. Calificaciones Máximas Absolutas.

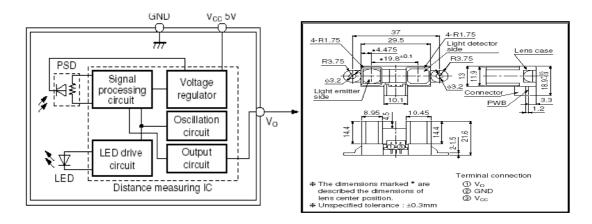

### **2.2.4.2. Sharp GP2Y0A02YK**

Es un sensor de infrarrojos que proporciona una lectura continua de la distancia medida como una tensión analógica dentro de un rango de 20 a 150 cm. La tensión de alimentación es de 5V y la tensión de salida varia unos 2 voltios de diferencia entre el margen mínimo y el máximo de la distancia medida. Tiene un encapsulado similar a otros sensores Sharp, pero presenta una mayor distancia entre la lente y el sensor con el fin de aumentar el rango de trabajo. La conexión se realiza mediante un conector JST de 3 vías, 2 para alimentación y una para la salida. La salida

está disponible de forma continua y su valor es actualizado cada 39 ms. Normalmente se conecta esta salida a la entrada de un convertidor analógico digital el cual convierte la distancia en un número que puede ser usado por el microprocesador.

Figura II. 7 Sensor Sharp.

Las aplicaciones son la detección de cuerpos humanos y aplicaciones en aparatos caseros.

Aquí presentamos el esquema interno de bloque las dimensiones del sensor y las calificaciones máximas absolutas.

Figura II. 8 Esquema interno y dimensiones del Sensor.

| Parameter                  | Symbol    | Rating                           | Unit |

|----------------------------|-----------|----------------------------------|------|

| Supply voltage             | $V_{CC}$  | -0.3 to +7                       | V    |

| *1 Output terminal voltage | $V_0$     | $-0.3$ to $V_{\rm CC}$ $\pm 0.3$ | V    |

| Operating temperature      | $T_{opr}$ | -10 to +60                       | °C   |

| Storage temperature        | $T_{stg}$ | -40 to +70                       | °C   |

Tabla II. II. Calificaciones Máximas Absolutas

# 2.2.4.3. La Familia GP2DXX

Los sensores infrarrojos Sharp GP2DXX son una familia de sensores infrarrojos para la detección y medida de distancia a los objetos. En la página Web de Sharp encontramos los modelos que se muestran en esta tabla refiriéndonos a ésta familia.

| Modelo     | Características Rangos absolutos Máximos                                                                                                                                      |               | Característica Electro-Opticas |                                                   |                                           |                         |                          |                        |

|------------|-------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|---------------|--------------------------------|---------------------------------------------------|-------------------------------------------|-------------------------|--------------------------|------------------------|

|            |                                                                                                                                                                               | VCC (V)       | Topr<br>(℃)                    | Rango de<br>distancia<br>de medida                | V <sub>OH</sub> (V)                       | V <sub>OL</sub> (V) MAX | Operativo<br>(mA)<br>MAX | Srandby<br>(μΑ)<br>MAX |

| GP2D02     | Sensor que mide<br>distancias con PSD<br>(Detector Sensible a la<br>Posición), LED infrarrojo<br>y circuito de procesado<br>de señal , 8 bits.                                | -0.3 a<br>+10 | -10 a<br>+60                   | 100 a 800                                         | V <sub>cc</sub> -0.3                      | 0.3                     | 17                       | 8                      |

| GP2D021    | Sensor que mide<br>distancias con PSD<br>(Detector Sensible a la<br>Posición), LED infrarrojo<br>y circuito de procesado<br>de señal , 8 bits.                                | -0.3 a<br>+10 | -10 a<br>+60                   | 40 a 300                                          | V <sub>cc</sub> -0.3                      | 0.3                     | 35                       | 8                      |

| GP2D05     | Sensor que mide<br>distancias con PSD<br>(Detector Sensible a la<br>Posición), LED infrarrojo<br>y circuito de procesado<br>de señal , 1 bits.                                | -0.3 a<br>+10 | -10 a<br>+60                   | 100 a 800                                         | V <sub>cc</sub> -0.3                      | 0.3                     | 22                       | 8                      |

| GPD12      | Sensor que mide distancias con PSD (Detector Sensible a la Posición), LED infrarrojo y circuito de procesado de señal, valor analógico entre 0-3V dependiendo de la distancia | -0.3 a 7      | -10 a<br>+60                   | 100 a 800                                         | V <sub>0</sub> (TYP)<br>= 0.4V a<br>80 cm |                         | MAX.50                   |                        |

| GP2D120    | Sensor que mide distancias con PSD (Detector Sensible a la Posición), LED infrarrojo y circuito de procesado de señal, valor analógico entre 0-3V dependiendo de la distancia | -0.3 a 7      | -10 a<br>+60                   | 40 a 300                                          | V <sub>0</sub> (TYP)<br>= 0.4V a<br>30 cm |                         | MAX.50                   |                        |

| GP2D150A   | Sensor que mide<br>distancias con PSD<br>(Detector Sensible a la<br>Posición), LED infrarrojo<br>y circuito de procesado<br>de señal, valor digital (0<br>o 1)                | -0.3 a 7      | -10 a<br>+60                   | 30 a 300<br>(Detección<br>distancia<br>typ. 15cm) | V <sub>cc</sub> -0.3                      | 0.6                     | MAX.50                   |                        |

| GP2D150T   | Sensor que mide<br>distancias con PSD<br>(Detector Sensible a la<br>Posición), LED infrarrojo<br>y circuito de procesado<br>de señal, valor digital (0<br>o 1)                | -0.3 a7       | -10 a<br>+60                   | 30 a 300<br>(Detección<br>distancia<br>typ. 22cm) | V <sub>cc</sub> -0.3                      | 0.6                     | MAX.50                   |                        |

| GP2Y0D02YK | Sensor que mide largas<br>distancias con PSD<br>(Detector Sensible a la<br>Posición), LED infrarrojo<br>y circuito de procesado<br>de señal , valor digital (a<br>80 cm)      | -0.3 a 7      | -10 a<br>+60                   | 200 a 1500                                        | V <sub>cc</sub> -0.3                      | 0.6                     | MAX.50                   |                        |

Tabla II. III. Modelos de las Familias Sharp.

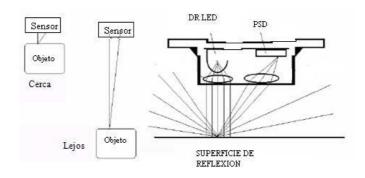

Como ya hemos dicho los sensores GP2DXX de Sharp son dispositivos de reflexión por infrarrojos con medidor de distancia proporcional al ángulo de recepción del haz de luz que incide en un sensor lineal integrado, dependiendo del modelo utilizado, la salida puede ser analógica digital o booleana.

El funcionamiento general de esta familia es el siguiente:

El dispositivo emite luz infrarroja por medio de un LED emisor de infrarrojos, esta luz pasa a través de una lente que concentra los rayos de luz formando un único rayo lo más concentrado posible para mejorar la directividad del sensor, la luz va recta hacia delante y cuando encuentra un obstáculo reflectante rebota y retorna con cierto ángulo de inclinación dependiendo de la distancia. La luz que retorna es concentrada por otra lente es concentrada por otra lente y así todos los rayos de luz inciden en un único punto del sensor de luz infrarroja que contiene en la parte receptora del dispositivo. Estos sensores constan de un CCD lineal que, dependiendo del ángulo de recepción de la luz, incidirá ésta en un punto u otro del sensor pudiendo de esta manera obtener un valor lineal y proporcional al ángulo de recepción del haz de luz.

Figura II. 9 Incidencia del haz de Luz.

Dependiendo del modelo elegido leeremos de una manera u otra la salida de éste con lo cual tendríamos que analizar el datasheet de cada modelo para ver su funcionamiento interno. Esto puede ser consultado en la página de Sharp o en webs especializadas.

En los modelos analógicos la salida es un voltaje proporcional a la distancia medida.

En los modelos digitales la lectura será de 8 bits serie con reloj externo.

En los modelos booleanos la salida será de 1 bit, éste marca el paso por la zona de histéresis del sensor con lo cual solo tendremos medición de una distancia fija.

#### 2.2.4.4. El sensor GP2D12.

El Sharp GP2D12 es un sensor medidor de distancias por infrarrojos que indica mediante una salida analógica la distancia medida. La tensión de salida varía de forma no lineal cuando se detecta un objeto en una distancia entre 10 y 80 cm. La salida está disponible de forma continua y su valor es actualizado cada 32 ms. Normalmente se conecta esta salida a la entrada de un convertidor analógico digital el cual convierte la distancia en un número que puede ser usado por el microprocesador. La salida también puede usada directamente en un circuito analógico. Hay que tener en cuenta que la salida no es lineal. El sensor utiliza solo una línea de salida para comunicarse con el procesador principal.

Figura II. 10 Sharp GP2D12 y su conector de tres pines.

Figura II. 11 Detalle del conector del Sensor.

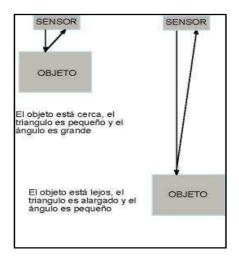

Este dispositivo emplea el método de triangulación utilizando un pequeño Sensor Detector de Posición (PSD) lineal para determinar la distancia o la presencia de los objetos dentro de su campo de visión.

Su modo de funcionamiento consiste en la emisión de un pulso de luz infrarroja, que se transmite a través de su campo de visión que se refleja contra un objeto. Si no encuentra ningún obstáculo, el haz de luz no refleja y en la lectura que se hace indica que no hay ningún obstáculo. En el caso de encontrar un obstáculo el haz de luz infrarroja se reflecta y crea un triángulo formado por el emisor, el punto de reflexión (el obstáculo) y el detector.

La información de la distancia se extrae midiendo el ángulo recibido. Si el ángulo es grande, entonces el objeto está cerca (el triángulo es ancho). Si el ángulo es pequeño significa que está lejos (el triángulo es largo y, por tanto, delgado).

Observemos a continuación esto (este precisamente es el concepto de triangularización):

Figura II. 12 Triangularización.

Observemos ahora como se lleva a cabo la triangulación en el sensor. El LED infrarrojo emite el haz de luz a través de una pequeña lente convergente que hace que el haz emisor llegue de forma paralela al objeto. Cuando la luz choca con un obstáculo, una cierta cantidad de luz se refleja, si el obstáculo fuera un espejo perfecto, todos los rayos del haz de luz pasarían y sería imposible medir la distancia. Sin embargo, casi todas las sustancias tienen un grado bastante grande de rugosidad de la superficie que produce una dispersión hemisférica de la luz (reflexión no teórica). Alguno de estos haces de ésta luz rebota hacia el sensor que es recibida por la lente.

La lente receptora también es una lente convexa, pero ahora sirve para un propósito diferente, actúa para convertir el ángulo de posición. Si un objeto se pone en el plano focal de una lente convexa y los otros rayos de luz paralelos en otro lado, el rayo que pasa por el centro de la lente atraviesa inalterado o marca el lugar focal. Los rayos restantes también enfocan a este punto.

En el plano focal hay un Sensor Detecto de Posición (PSD). Éste dispositivo semiconductor entrega una salida cuya intensidad es proporcional a la posición respecto al centro (eficaz) de la

luz que incide en él. El rendimiento del PSD en la salida es proporcional a la posición del punto focal. Esta señal analógica tratada es la que se obtiene a la salida del sensor.

Figura II. 13 Reflexión del Haz de Luz.

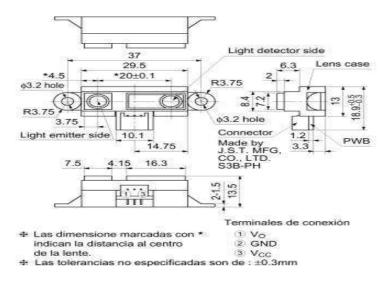

#### Características:

- ✓ Menor influencia del color de los objetos reflexivos.

- ✓ Línea indicadora de distancia output/distance:

- ✓ Tipo de salida indicadora de la distancia analógica (tensión analógica). Distancia del detector de 10 a 80 cm.

- ✓ Bajo costo.

Figura II. 14 Dimensiones y Encapsulado.

# Aplicaciones:

- ✓ En televisiones

- ✓ Computadoras Personales

- ✓ Automóviles

- √ Fotocopiadoras

- ✓ Sensores en sanitarios

- ✓ Sensores de cuerpo humano para los productos de consumo como ventiladores eléctricos y aires acondicionados.

- ✓ Sensores de garaje

Para

$$Ta = 25^{\circ} C y VCC = 5V$$

| Parámetro                        | Símbolo          | Rangos                      | Unidades               |

|----------------------------------|------------------|-----------------------------|------------------------|

| Tensión de Alimentación          | $V_{CC}$         | -0.3 a 7                    | V                      |

| Tensión en el terminal de salida | V <sub>O</sub>   | -0.3 a V <sub>CC</sub> +0.3 | V                      |

| Temperatura de trabajo           | Topr             | -10 a +60                   | °C                     |

| Temperatura de almacenamiento    | T <sub>stg</sub> | -40 a +70                   | $^{\circ}\!\mathrm{C}$ |

Tabla II. IV. Valores Máximos Absolutos.

| Parámetro                          | Símbolo | Rangos     | Unidades |

|------------------------------------|---------|------------|----------|

| Tensión de alimentación de trabajo | Vcc     | 4.5 a +5.5 | V        |

Tabla II. V. Condiciones de Trabajo Recomendadas.

| Parámetros                                   |        | Símbolo            | Condiciones                               | MIN.              | TIP. | MAX. | Unidad |

|----------------------------------------------|--------|--------------------|-------------------------------------------|-------------------|------|------|--------|

| Rango de medida de distancia                 |        | $\Delta L$         | (*1) (*3)                                 | 10                | -    | 80   | cm     |

| Tensión en el terminal                       | GP2D12 | V <sub>O</sub>     | L=80 cm (*1)                              | 0.25              | 0.4  | 0.55 | V      |

| de salida                                    | GP2D15 | V <sub>OH</sub>    | Tensión de<br>salida a nivel<br>alto (*1) | V <sub>CC</sub> - |      |      | V      |

|                                              |        | V <sub>OL</sub>    | Tensión de<br>salida a nivel<br>bajo (*1) |                   |      | 0.6  | V      |

| Incremento de la tensión de salida           | GP2D12 | $\Delta V_{\rm O}$ | Cambio de<br>salida de L=80 a<br>10 cm    | 1.75              | 2.0  | 2.25 | V      |

| Tensión de salida en función de la distancia | GP2D15 | Vo                 | (*1)(*2)(*4)                              | 21                | 24   | 27   | cm     |

| Corriente media de dispe                     | rsión  | $I_{CC}$           | L = 80 cm (*1)                            |                   | 33   | 50   | mA     |

Tabla II. VI. Características Electro- Ópticas.

✓ \*1. Objeto reflexivo usando: Papel blanco (Para el color gris se usa la tarjeta R-27 de la

Cía. de Kodak S.A. · la cara blanca, la proporción reflexiva; 90%).

- ✓ \*2. Utilizamos el dispositivo después del ajuste siguiente: salida al cambiar la distancia

L 24cm±3cm debe medirse por el sensor.

- √ \*3. Rango de distancia que mide el sistema del sensor óptico.

- ✓ \*4. La salida de cambio tiene una anchura de la histéresis. La distancia especificada por

Vo desde que la salida a nivel bajo (L) hasta que cambia a nivel alto (H).

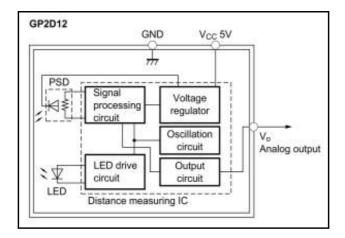

Figura II. 15 Bloques Internos.

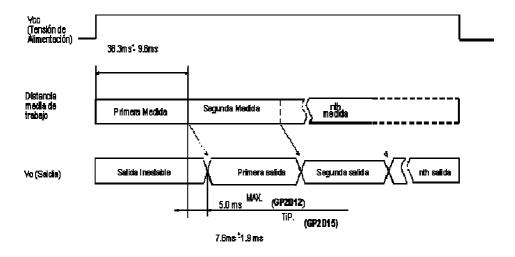

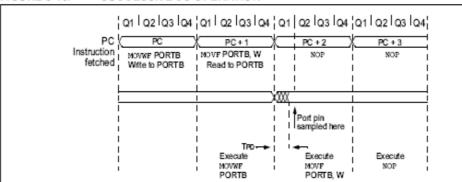

Figura II. 16 Cronograma.

Figura II. 17 Características de Distancias.

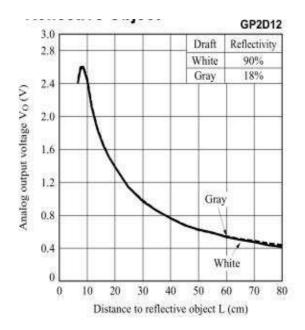

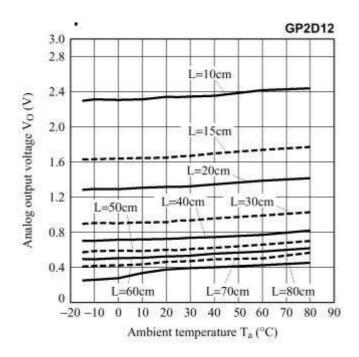

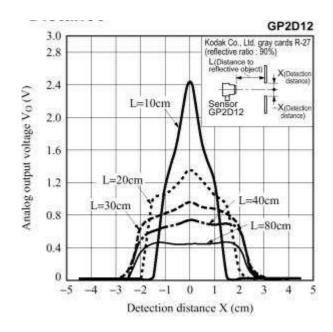

# 2.2.4.4.1. Curvas Características del GP2D12

Figura II. 18 Tensión de Salida Analógica en función de Superficie Iluminada del Objeto Reflexivo

Figura II. 19 Tensión de Salida Analógica en función de la Distancia al objeto reflexivo

Figura II. 20 Tensión de Salida Analógica en función de la Temperatura Ambiente.

Figura II. 21 Tensión de Salida Analógica en función de la distancia de detección.

# 2.3. LOS SISTEMAS DE COMUNICACIÓN

El conjunto de elementos que intervienen en el proceso de intercambio de información forma un sistema de comunicación.

# 2.3.1. TRANSMISIÓN DE ONDAS DE RADIO

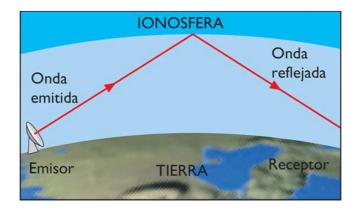

Figura II. 22. Reflexión de las ondas en la ionosfera

Las ondas electromagnéticas se propagan en línea recta. En consecuencia, si pretendemos enviar una señal de radio a larga distancia, dado que la Tierra tiene una superficie redondeada, la señal se alejará de la superficie de la Tierra y se perderá en el espacio. Sin embargo, las ondas de radio tienen la propiedad de reflejarse en las capas altas de la atmósfera, en concreto en la ionosfera.

La primera vez que se realizó una transmisión de radio a larga distancia fue en 1901. Entonces se desconocía la existencia de la ionosfera. Fue Marconi quien dispuso un transmisor y un receptor a ambos lados del Atlántico, entre Cornualles, en Inglaterra, y Terranova, en Canadá. Tras el éxito del experimento, Oliver Heavyside.

Kennelly descubrieron la existencia de la ionosfera y sus propiedades como reflectante de señales de cierta banda de frecuencias.

La ionosfera es la capa de la atmósfera situada entre los 90 y los 400 km de altura. Presenta la particularidad de que en ella los átomos se ionizan y liberan electrones por efecto de la luz solar. Según la concentración de iones, la ionosfera se puede dividir en varias capas, que se comportan de diferente forma ante la reflexión de las ondas. En cierto modo, al existir una nube electrónica en la ionosfera, esta se comporta como una pantalla para las señales eléctricas. No obstante, dependiendo de dicha concentración, existirá mayor o menor «blindaje» frente a las señales.

| Capa de<br>Ionosfera | Características de la capa                                                                                         | Rango frecuencias<br>que refleja |

|----------------------|--------------------------------------------------------------------------------------------------------------------|----------------------------------|

| Capa D               | Capa apenas ionizada, únicamente refleja las frecuencias más bajas, debilitando las señales de frecuencias medias. | 0-3 MHz                          |

| Capas E-F | Son dos capas de características similares, con igual comportamiento frente a las señales. Están situadas entre los 120 y 150 km, y reflejan las señales de frecuencia media. La reflexión de la señal depende de las variaciones en la concentración iónica entre el día, debido a la incidencia de la luz solar, y la noche, cuando decrece la concentración. | 3-8 MHz  |

|-----------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------|

| Capa F'   | Es la capa más importante por la gran concentración de iones, cubriendo un espesor de hasta los 500 km.                                                                                                                                                                                                                                                         | 8-15 MHz |

Tabla II. VII. Características de las capas de la tierra

Las ondas reflejadas en la ionosfera que vuelven a la Tierra pueden ser de nuevo emitidas hacia el espacio y sufrir una segunda reflexión en la ionosfera. De hecho, este proceso se puede repetir sucesivas veces, de manera que las ondas podrán salvar grandes distancias gracias a las continuas reflexiones. Incluso, si se emite una señal con potencia y frecuencia adecuada, es posible que las ondas circunden la Tierra.

Por otra parte, no todas las frecuencias rebotan en la ionosfera. Las señales con frecuencias superiores a 15 MHz «escapan» a la reflexión de la atmósfera. Este es el rango de las señales de alta frecuencia (HF), de muy alta frecuencia (VHF), de ultra-alta frecuencia (UHF), así como de frecuencias superiores como las microondas. Este tipo de señales solo puede utilizarse para comunicaciones a corta distancia mediante estaciones terrestres repetidoras. Para salvar mayores distancias sería necesario recurrir al uso de satélites de comunicaciones.

# 2.3.2. COMPONENTES DE UN SISTEMA DE COMUNICACIÓN

En todo sistema de comunicación podemos distinguir los siguientes componentes:

- Emisor: es el elemento que transmite la información.

- **Receptor:** es el elemento que recibe la información.

- Canal: es el medio a través del cual tiene lugar el trasvase de información entre el emisor y el receptor.

Figura II. 23. Sistema de comunicación

El emisor y el receptor pueden encontrarse a unos pocos metros de distancia o bien estar alejados cientos e incluso miles de kilómetros, como ocurre en los sistemas de telecomunicaciones vía satélite o en los vuelos espaciales.

# 2.3.3. COMUNICACIÓN INALÁMBRICA

La comunicación inalámbrica (inglés *wireless*, sin cables) es aquella en la que extremos de la comunicación (emisor/receptor) no se encuentran unidos por un medio de propagación físico, sino que se utiliza la modulación de ondas electromagnéticas a través del espacio. En este sentido, los dispositivos físicos sólo están presentes en los emisores y receptores de la señal, entre los cuales encontramos: antenas, computadoras portátiles, PDA, teléfonos móviles, etc.<sup>1</sup>

## 2.3.3.1. Aspecto histórico y generalidades

La comunicación inalámbrica, que se realiza a través de ondas de radiofrecuencia, facilita la operación en lugares donde la computadora no se encuentra en una ubicación fija (almacenes, oficinas de varios pisos, etc.); pero se trata de una tecnología sometida a investigación que en el futuro será utilizada de forma general.

Cabe también mencionar actualmente que las redes cableadas presentan ventaja en cuanto a transmisión de datos sobre las inalámbricas. Mientras que las cableadas proporcionan velocidades de hasta 1 Gbps (Red Gigabit), las inalámbricas alcanzan sólo hasta 108 Mbps.

Se puede realizar una "mezcla" entre inalámbricas y alámbricas, de manera que pueden funcionar de la siguiente manera: que el sistema cableado sea la parte principal y la inalámbrica sea la que le proporcione movilidad al equipo y al operador para desplazarse con facilidad en distintos campos (almacén u oficina).

Un ejemplo de redes a larga distancia son las Redes públicas de Conmutación por Radio. Estas redes no tienen problemas en pérdida de señal, debido a que su arquitectura está diseñada para soportar paquetes de datos en vez de comunicaciones por voz.

Actualmente, las transmisiones inalámbricas constituyen una eficaz herramienta que permite la transferencia de voz, datos y vídeo sin la necesidad de cableado. Esta transferencia de información es lograda a través de la emisión de ondas de radio teniendo dos ventajas: movilidad y flexibilidad del sistema en general.

En general, la tecnología inalámbrica utiliza ondas de radiofrecuencia de baja potencia y una banda específica, de uso libre para transmitir, entre dispositivos.

# 2.3.3.2. Campos de Utilización

La tendencia a la movilidad y la difusión hacen que cada vez sean más utilizados los sistemas inalámbricos, y el objetivo es ir evitando los cables en todo tipo de comunicación, no solo en el campo informático sino en televisión, telefonía, seguridad, etc.

### 2.3.3.3. Algunos problemas asociados con la tecnología inalámbrica

Los hornos de microondas utilizan radiaciones en el espectro de 2,45 Ghz. Es por ello que las redes y teléfonos inalámbricos que utilizan el espectro de 2,4 Ghz. pueden verse afectados por la proximidad de este tipo de hornos, que pueden producir interferencias en las comunicaciones. Otras veces, este tipo de interferencias provienen de una fuente que no es accidental. Mediante el uso de un perturbador o inhibidor de señal se puede dificultar e incluso imposibilitar las comunicaciones en un determinado rango de frecuencias.

# 2.3.3.4. Equipo inalámbrico

Son los equipos de punto de acceso que normalmente vienen con antena omni 2 Dbi, muchas veces desmontables, en las cuales se puede hacer enlaces por encima de los 500 metros y además se pueden interconectar entre sí. No debe haber obstáculos para que la señal sea excelente, ya que esto interfiere en la señal y puede haber problemas en la conexión.

# 2.4. RED INALÁMBRICA

El término red inalámbrica (Wireless network) en inglés es un término que se utiliza en informática para designar la conexión de nodos sin necesidad de una conexión física (cables), ésta se da por medio de ondas electromagnéticas. La transmisión y la recepción se realizan a través de puertos.

Una de sus principales ventajas es notable en los costos, ya que se elimina todo el cable ethernet y conexiones físicas entre nodos, pero también tiene una desventaja considerable ya que para este tipo de red se debe de tener una seguridad mucho más exigente y robusta para evitar a los intrusos. En la actualidad las redes inalámbricas son una de las tecnologías más prometedoras.

# 2.4.1. Categorías

Existen dos categorías de las redes inalámbricas.

- 1. **Larga distancia:** estas son utilizadas para distancias grandes como puede ser otra ciudad u otro país.

- Corta distancia: son utilizadas para un mismo edificio o en varios edificios cercanos no muy retirados.

# 2.4.2. Aplicaciones

✓ Las bandas más importantes con aplicaciones inalámbricas, del rango de frecuencias que abarcan las ondas de radio, son la VLF (comunicaciones en navegación y submarinos), LF (radio AM de onda larga), MF (radio AM de onda media), HF (radio AM de onda corta), VHF (radio FM y TV), UHF (TV).

- ✓ Mediante las microondas terrestres, existen diferentes aplicaciones basadas en protocolos como Bluetooth o ZigBee para interconectar ordenadores portátiles, teléfonos u otros aparatos. También se utilizan las microondas para comunicaciones con radares (detección de velocidad u otras características de objetos remotos) y para la televisión digital terrestre.

- ✓ Las microondas por satélite se usan para la difusión de televisión por satélite, transmisión telefónica a larga distancia y en redes privadas, por ejemplo.

- ✓ Los infrarrojos tienen aplicaciones como la comunicación a corta distancia de los ordenadores con sus periféricos. También se utilizan para mandos a distancia, ya que así no interfieren con otras señales electromagnéticas, por ejemplo la señal de televisión. Uno de los estándares más usados en estas comunicaciones es el IrDA (*Infrared Data Association*). Otros usos que tienen los infrarrojos son técnicas como la tomografía, la cual permite determinar la temperatura de objetos a distancia.

#### 2.5. RADIOFRECUENCIA

También llamada espectro de radiofrecuencia o RF, se aplica a la porción menos energética del espectro electromagnético situado entre 3 Hz y 300GHz.

Las ondas electromagnéticas pueden transmitirse aplicando la corriente alterna originada en un generador a una antena.

#### 2.5.1. Características Generales

Permite comunicaciones de corto y medio alcance, puede atravesar obstáculos y paredes, el campo de aplicación es muy grande.

Dentro del rango de frecuencias que abarca dicha tecnología, únicamente nos interesa el rango de frecuencias que va de 30-3000MHz y cuya longitud de onda es de 1m-100mm, ya que es la banda donde encontramos las comunicaciones inalámbricas.

Esta tecnología no tiene un protocolo establecido, es por eso que no tiene unas características generales, una arquitectura de funcionamiento, etc, hecho que también la hace más versátil y dependiente de las características del dispositivo utilizado en la comunicación.

Para poder establecer una comunicación multipunto es necesario crear un protocolo que permita el intercambio de información entre los diferentes dispositivos.

Este protocolo debe contener tanto unos bits asignados a la información que quiere transmitirse, como unos bits que indiquen el dispositivo receptor de la información, bits de error para evitar pérdidas de comunicación, bits destinados a definir la modulación de dicha información, etc.

El protocolo RF más usado para la comunicación inalámbrica de dispositivos es el RS- 232. La velocidad de transmisión y de recepción de información depende en exclusiva de los dispositivos utilizados. Para evitar interferencias la velocidad de transmisión no debe superar los 4800Baudios y la de recepción los 2400Baudios. Como el mismo dispositivo integra tanto transmisor como receptor, el baud rate máximo para evitar las interferencias está, alrededor de los 2400Baudios.

## 2.5.2. Tipos de Comunicaciones Inalámbricas por RF

Las transmisiones de datos entre equipos electrónicos sin cables se están aplicando cada vez más debido a los medios tecnológicos actuales, que son los circuitos integrados que permiten hacer un diseño sin tener demasiados conocimientos de RF, ni disponer de cada instrumentación para RF, ya que estos dispositivos requieren pocos componentes externos y ningún tipo de ajuste en RF.

Primero se usaron módulos de RF con componentes discretos unidireccionales y precisamente para no tener que depender del diseño de una circuitería en RF. Posteriormente con la aparición de circuitos transmisores completamente integrados con las funciones de emisor y receptor, en diferentes bandas de frecuencia que se fueron estandarizando en las diferentes zonas (Europa y USA), han permitido poderlos utilizar en los diferentes campos de aplicación industrial, comercial, y medico, como: control remoto, transmisión de datos en sensores o sistemas de adquisición de datos, en monitorización médica o de la salud, etc.

Las comunicaciones inalámbricas por RF se pueden dividir en las que no cumplen ningún protocolo estándar y las que cumplen un protocolo estándar, y en las normativas sobre sus distintas frecuencias de trabajo, que a la vez definen velocidad de transmisión o ancho de banda y campo de aplicación.

#### 2.6. MOTORES

Un motor eléctrico es una máquina eléctrica que transforma energía eléctrica en energía mecánica por medio de interacciones electromagnéticas.

#### 2.6.1. Servo Motores HITEC HS-311

Figura II. 24. Servomotor

Es un aparato destinado a vencer grandes resistencias, mediante la amplificación de fuerzas aplicadas, relativamente más pequeñas; que consta de dos bombines hidráulicas.

El servomotor mostrado en la Figura II.24 fue diseñado como un actuador mecánico en cualquier sistema de servomecanismo que tiene por objeto llevar al sistema a una lectura cero, es decir la señal de error se redujo a cero, y existen dos tipos de servomotores, de corriente directa y de corriente alterna.

Sus características fundamentales para cd y ca se basaron en lo siguiente: la primera radicó en que el par de salida del motor sea aproximadamente proporcional a su voltaje de control aplicado y la segunda se basa en el hecho de que la dirección del par éste determinada por la polaridad instantánea del voltaje de control. El servomotor de de campo controlado es aquel donde el par que produjo este motor es cero cuando el amplificador de error de de no le suministra excitación de campo, y si se invierte la polaridad del campo, se invierte la dirección del motor.

#### 2.6.1.1. Características

| Velocidad:     | 0.23 seg/60 grados (260 grados/seg) |

|----------------|-------------------------------------|

| Par de salida: | 3.7 Kg-cm                           |

| Dimensiones:   | 40 x 20 x 37 mm                     |

| Peso:          | 43 gr                               |

| Frec. PWM:     | 60Hz (20ms)                         |

| Rango giro:    | 180 grados                          |

Tabla II. VIII. Características de las capas de la tierra

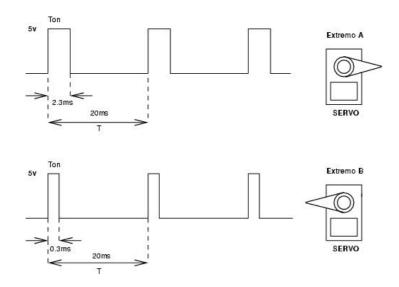

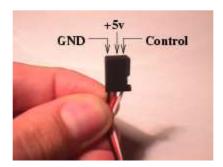

#### 2.6.1.2. Control

Los servos se controlan aplicando una señal PWM por su cable de control. Las señales PWM (Pulse Width Modulation, Modulación por anchura de pulso) son digitales (pueden valer 0 ó 1) y permiten que usando un único pin de un microcontrolador podamos posicionar el servo. Esto es una gran ventaja, porque si por ejemplo, disponemos de un micro con 8 pines de salida, podremos posicionar 8 servos.

Figura II. 25. Ancho de Pulso